## บรรณานุกรม

## ภาษาไทย

สมศักดิ์ เตชะเศรษฐ์ธนะ. เทเลเท็กซ์ (การส่งข่าวสารอิเลคทรอนิคส์). <u>เซมิคอนดัคเตอร์ อิเลคทรอนิคส์.</u> 75 (กุมภาพันธ์ 2530): 164-175.

ชวัช เมฆสวรรค์,คร. และ ซาวามูระ,โยชิคะซึ. <u>เทคนิคการซ่อมเครื่องรับ โทรทัศน์สี.</u> กรุงเทพมหานคร: กุรุสภาลาคพร้าว, 2533.

เทเลอิมฟอร์เมชั่น,บริษัท,จำกัด.<u>เอกสารแนะนำระบบเทเลเทกซ์.</u>กรุงเทพฯ,ม.ป.ป.

เจน สงสมพันธุ์, นิคม อนันตทิพย์. <u>เทคโนโลยีโทรทัศน์</u>.เอดิสันเพรสโพรดักส์.กรุงเทพ,2533

# <u>ภาษาอังกฤษ</u>

Zorkoezy, Peter. Information Technology An Introduction. New York: VAN NOSTRAND REINHOLD. 1984.

Money, Streve, A. Teletext and Viewdata. Newnes Technical Book. n.d.

Kinghorn, J.R. Enhanced Computer Controlled Teletext SAA5243 Series User Manual.

English: Micham, 1989. 143 pp.

ภาคผนวก

ภาคผนวก ก. I<sup>2</sup>C Bus Specification

| Contents - The I <sup>2</sup> C-bus Specification                                                                                                                                   | Page   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 1.0 Introduction                                                                                                                                                                    | 1      |

| 2.0 The I <sup>2</sup> C-bus concept                                                                                                                                                | 1      |

| 3.0 General characteristics                                                                                                                                                         | 5      |

| 4.0 Bit transfer 4.1 Data validity 4.2 START and STOP conditions                                                                                                                    | 5      |

| 5.0 Transferring data 5.1 Byte format 5.2 Acknowledge                                                                                                                               | 5      |

| <ul> <li>6.0 Arbitration and clock generation</li> <li>6.1 Synchronization</li> <li>6.2 Arbitration</li> <li>6.3 Use of the clock synchronizing mechanism as a handshake</li> </ul> | 7      |

| 7.0 Formats                                                                                                                                                                         | 10     |

| 8.0 Addressing 8.1 Definition of bits in the first byte 8.1.1 General call address 8.1.2 Start byte 8.1.3 CBUS compatibility                                                        | 13     |

| 9.0 Electrical specifications of inputs and outputs of I <sup>2</sup> C-bus interface                                                                                               | ces 19 |

| 10.0 Timing                                                                                                                                                                         | 21     |

| 11.0 'Low-speed' mode 11.1 START and STOP conditions 11.2 Data format and timing                                                                                                    | 23     |

| Appendix A - Values of resistors R <sub>p</sub> and R <sub>s</sub>                                                                                                                  | 2      |

| Appendix B - Note to section 6.2                                                                                                                                                    | 2      |

Full details of Philips'  $I^2C$ -bus compatible ICs is given in Data Handbook IC12, ordering code 9398 153 10011

Purchase of Philips' I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specification defined by Philips.

# 1.0 Introduction

For 8-bit applications, such as those requiring single-chip microcomputers, certain design criteria can be established:

- · A complete system usually consists of at least one microcomputer and other peripheral devices such as memories and I/O expanders.

- The cost of connecting the various devices within the system must be kept to a

- Such a system usually performs a control function and doesn't require high-speed data transfer.

- Overall efficiency depends on the devices chosen and the interconnecting bus structure.

To produce a system to satisfy these criteria, a serial bus structure is needed. Although serial buses don't have the throughput capability of parallel buses, they do require less wiring and fewer connecting pins. However, a bus is not merely an interconnecting wire, it embodies all the formats and procedures for communication within the system.

ICs communicating with each other on a serial bus must have some form of protocol which avoids all possibilities of confusion, data loss and blockage of information. Fast ICs must be able to communicate with slow ICs. The system must not be dependent on the ICs connected to it, otherwise modifications or improvements would be impossible. A procedure has also to be devised to decide which IC will be in control of the bus and when. And if different ICs with different clock speeds are connected to the bus - the bus clock source must be defined.

. All these criteria are involved in the specification of the I<sup>2</sup>C-bus.

# 2.0 The I2C-bus concept

The I<sup>2</sup>C-bus supports ICs manufactured with any process (NMOS, CMOS, I<sup>2</sup>L). Two wires, serial data (SDA) and serial clock (SCL) carry information between the ICs connected to the bus. Each IC is recognised by a unique address - whether it's a microcomputer, LCD driver, memory or keyboard interface - and can operate as either a transmitter or receiver, depending on the function of the ICs we're considering. Obviously an LCD driver is only a receiver, while a memory can both receive and transmit data. In addition to transmitters and receivers, ICs can also be considered as masters or slaves when performing data transfers (see Table 1). A master is the IC which initiates a data transfer on the bus and generates the clock signals to permit that transfer. At that time, any IC addressed is considered a slave.

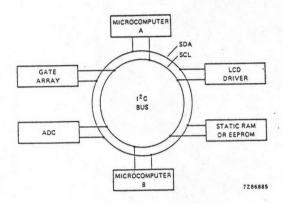

The I<sup>2</sup>C-bus is a multi-master bus. This means that more than one IC capable of controlling the bus can be connected to it. As masters are usually microcomputers, let's consider the case of a data transfer between two microcomputers connected to the I<sup>2</sup>C-bus (Fig.1). This highlights the master-slave and receiver-transmitter relationships to be found on the I2C-bus. It should be noted that these relationships are not permanent, but only depend on the direction of data transfer at that time. The transfer of data would proceed as follows:

Fig.1 Typical I<sup>2</sup>C-bus configuration

- 1) Suppose microcomputer A wants to send information to microcomputer B:

- microcomputer A (master), addresses microcomputer B (slave)

- microcomputer A (master transmitter), sends data to microcomputer B (slave receiver)

- microcomputer A terminates the transfer.

- 2) If microcomputer A wants to receive information from microcomputer B:

- microcomputer A (master) addresses microcomputer B (slave)

- microcomputer A (master receiver) receives data from microcomputer B (slave transmitter)

- microcomputer A terminates the transfer.

Even in this case, the master (microcomputer A) generates the timing and

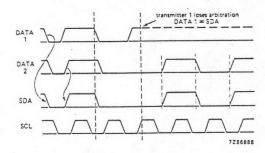

The possibility of connecting more than one microcomputer to the I<sup>2</sup>C-bus means terminates the transfer. that more than one master could try to initiate a data transfer at the same time. To avoid the chaos that might ensue from such an event - an arbitration procedure has been developed. This procedure relies on the wired-AND connection of all I2C

If two or more masters try to put information onto the bus, the first to produce interfaces to the I2C-bus. a 'one' when the other produces a 'zero' will lose the arbitration. The clock signals during arbitration are a synchronised combination of the clocks generated by the masters using the wired-AND connection to the SCL line (for more detailed information concerning arbitration see section 6.0).

Generation of clock signals on the I<sup>2</sup>C-bus is always the responsibility of master ICs; each master generates its own clock signals when transferring data on the bus. Bus clock signals from a master can only be altered when they are stretched by a slow-slave IC holding-down the clock line, or by another master when arbitration takes place.

Table 1 Definition of I<sup>2</sup>C-bus terminology

| Transmitter:  | the IC which sends data to the bus                                                                                                                      |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receiver:     | the IC which receives data from the bus                                                                                                                 |

| Master:       | the IC which initiates a transfer, generates clock signals and terminates a transfer                                                                    |

| Slave:        | the IC addressed by a master                                                                                                                            |

| Multi-master: | more than one master can attempt to control the bus at the same time without corrupting the message                                                     |

| Arbitration:  | procedure to ensure that if more than one master simultaneously tries to control the bus, only one is allowed to do so and the message is not corrupted |

| Synchronizati | on: procedure to synchronize the clock signals of two or more                                                                                           |

| 5,110122      | ICs                                                                                                                                                     |

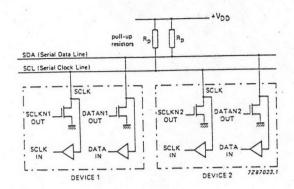

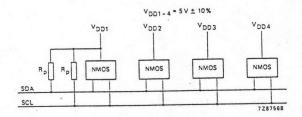

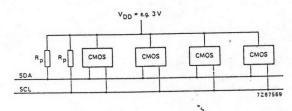

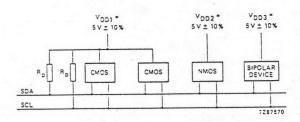

Fig.2 Connection of I<sup>2</sup>C interfaces to the I<sup>2</sup>C-bus

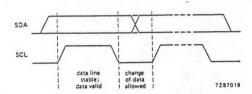

Fig.3 Bit transfer on the I<sup>2</sup>C-bus

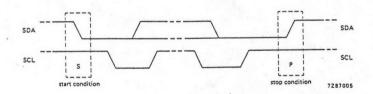

Fig.4 START and STOP conditions

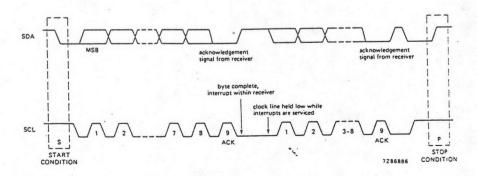

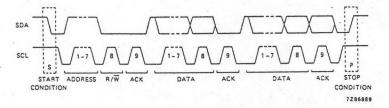

Fig.5 Data transfer on the I<sup>2</sup>C-bus

## 3.0 General characteristics

Both SDA and SCL are bidirectional lines, connected to a positive supply voltage via a pull-up resistor (see Fig.2). When the bus is free, both lines are HIGH. The output stages of I<sup>2</sup>C interfaces connected to the bus must have an open-drain or open-collector to perform the wired-AND function. Data on the I<sup>2</sup>C-bus can be transferred at a rate up to 100 kbit/s. The number of interfaces connected to the bus is solely dependent on the limiting bus capacitance of 400 pF.

#### 4.0 Bit transfer

Due to the variety of different technology ICs (CMOS, NMOS,  $I^2L$ ) which can be connected to the  $I^2C$ -bus, the levels of the logical '0' (LOW) and '1' (HIGH) are not fixed and depend on the associated level of  $V_{DD}$  (see section 9.0 for Electrical specifications). One clock pulse is generated for each data bit transferred.

#### 4.1 Data validity

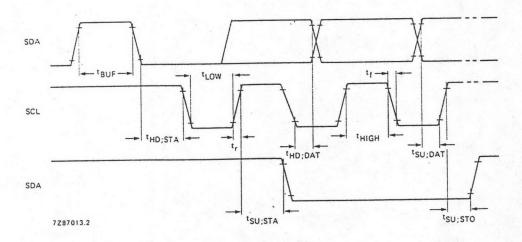

The data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW (Fig.3).

#### 4.2 START and STOP conditions

Within the procedure of the  $I^2$ C-bus, unique situations arise which are defined as START and STOP conditions (see Fig.4).

A HIGH to LOW transition of the SDA line while SCL is HIGH is one such unique case. This situation indicates a START condition.

A LOW to HIGH transition of the SDA line while SCL is HIGH defines a STOP condition.

START and STOP conditions are always generated by the master. The bus is considered to be busy after the START condition. The bus is considered to be free again a certain time after the STOP condition. This bus free situation will be described in detail later (in section 10.0).

Detection of START and STOP conditions by ICs connected to the bus is easy if they incorporate the necessary interfacing hardware. However, microcomputers with no such interface have to sample the SDA line at least twice per clock period to sense the transition.

### 5.0 Transferring data

#### 5.1 Byte format

Every byte put on the SDA line must be 8-bits long. The number of bytes that can be transmitted per transfer is unrestricted. Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit (MSB) first (Fig.5). If a receiver can't receive another complete byte of data until it has performed some other function, for example, servicing an internal interrupt, it can hold the clock line SCL LOW to force the transmitter into a wait state. Data transfer then continues when the receiver is ready for another byte of data and releases clock line SCL.

In some cases, it's permissible to use a different format from the I<sup>2</sup>C-bus format (for CBUS compatible ICs for example). A message which starts with such an address can be terminated by generation of a STOP condition, even during the transmission of a byte. In this case, no acknowledge is generated (see section 8.4).

Fig.6 Acknowledge on the I<sup>2</sup>C-bus

Fig.7 Clock synchronization during the arbitration procedure

## 5.2 Acknowledge

Data transfer with acknowledge is obligatory. The acknowledge-related clock pulse is generated by the master. The transmittier releases the SDA line (HIGH) during the acknowledge clock pulse.

The receiver has to pull down the SDA line during the acknowledge clock pulse so that it remains stable LOW during the high period of this clock pulse (Fig.6). Of course, set-up and hold times must also be taken into account and these will be described in section 10.0.

Usually, a receiver which has been addressed is obliged to generate an acknowledge after each byte has been received (except when the message starts with an RC-5 or CBUS address - see section 8.1.3).

When a slave receiver doesn't acknowledge on the slave address (for example, it's unable to receive because it's performing some real-time function), the data line has to be left HIGH by the slave. The master can then generate a STOP condition to abort the transfer.

If a slave receiver acknowledges the slave address but, some time later in the transfer cannot receive any more data bytes, the master must again about the transfer. This is indicated by the salve not generating the acknowledge on the first byte to follow. The slave leaves the data line HIGH and the master generates the STOP condition.

If a master receiver is involved in a transfer, it must signal the end of data to the slave transmitter by not generating an acknowledge on the last byte that was clocked out of the slave. The slave transmitter must release the data line to allow the master to generate the STOP condition.

# 6.0 Arbitration and clock generation

## 6.1 Synchronization

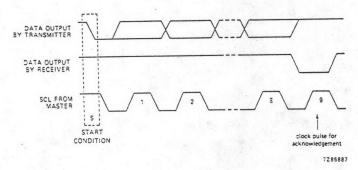

All masters generate their own clock on the SCL line to transfer messages on the  $I^2$ C-bus. Data is only valid during the clock HIGH period. A defined clock is therefore needed for the bit-by-bit arbitration procedure to take place.

Clock synchronization is performed using the wired-AND connection of I<sup>2</sup>C interfaces to the SCL line. This means that a HIGH to LOW transition on the SCL line will cause the ICs concerned to start counting off their LOW period and, once an IC clock has gone LOW, it will hold the SCL line in that state until the clock HIGH state is reached (Fig.7). However, the LOW to HIGH transition of this clock may not change the state of the SCL line if another clock is still within its LOW period. The SCL line will therefore be held LOW by the IC with the longest LOW period. ICs with shorter LOW periods enter a HIGH wait-state during this time.

When all ICs concerned have counted off their LOW period, the clock line will be released and go HIGH. There will then be no difference between the IC clocks and the state of the SCL line and all the ICs will start counting their HIGH periods. The first IC to complete its HIGH period will again pull the SCL line LOW.

In this way, a synchronised SCL clock is generated with its LOW period determined by the IC with the longest clock LOW period, and its HIGH period determined by the one with the shortest clock HIGH period.

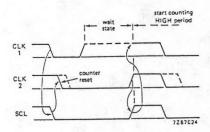

# 6.2 Arbitration (see also Appendix B)

Arbitration takes place on the SDA line in such a way that the master which transmits a HIGH level, while another master is transmitting a LOW level will

Fig.8 Arbitration procedure of two masters

Fig.9 A complete data transfer

switch off its DATA output stage because the level on the bus doesn't correspond to its own level.

Arbitration can continue for many bits. Its first stage is comparison of the address bits (addressing information is in section 8.0). If the masters are each trying to address the same IC, arbitration continues with comparison of the data. Because address and data information on the I<sup>2</sup>C-bus is used for arbitration, no information is lost during this process.

A master which loses the arbitration can generate clock pulses until the end of the byte in which it loses the arbitration.

If a master loses arbitration during the addressing stage, it's possible that the winning master is trying to address it. The losing master must therefore switch over immediately to its slave receiver mode.

Figure 8 shows the arbitration procedure for two masters. Of course, more may be involved (depending on how many masters are connected to the bus). The moment there is a difference between the internal data level of the master generating DATA 1 and the actual level on the SDA line, its data output is switched off, which means that a HIGH output level is then connected to the bus. This will not affect the data transfer initiated by the winning master. Since control of the I<sup>2</sup>C-bus is decided solely on the address and data sent by competing masters, there is no central master, nor any order of priority on the bus.

### 6.3 Use of the clock synchronising mechanism as a handshake

In addition to being used during the arbitration procedure, the clock synchronization mechanism can be used to enable receivers to cope with fast data transfers, on either a byte level or a bit level.

On the byte level, an IC may be able to receive bytes of data at a fast rate, but needs more time to store a received byte or prepare another byte to be transmitted. Slaves can then hold the SCL line LOW after reception and acknowledgement of a byte to force the master into a wait state until the slave is ready for the next byte transfer in a type of handshake procedure.

On the bit level, an IC such as a microcomputer without a hardware I<sup>2</sup>C interface on-chip can slow down the bus clock by extending each clock LOW period. In this way, the speed of any master is adapted to the internal operating rate of this IC.

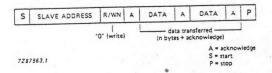

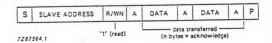

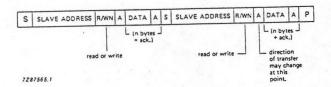

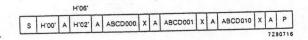

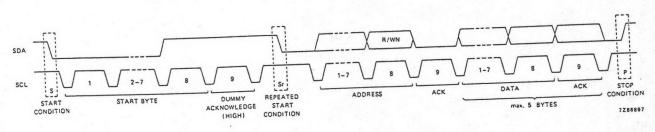

#### 7.0 Formats

Data transfers follow the format shown in Fig.9. After the START condition, a slave address is sent. This address is 7 bits long, the eighth bit is a data direction bit  $(R/\overline{W})$  - a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a STOP condition generated by the master. However, if a master still wishes to communicate on the bus, it can generate another START condition and address another slave without first generating a STOP condition. Various combinations of read/write formats are then possible within such a transfer.

Possible data transfer formats are:

a) Master transmitter transmits to slave receiver. Direction is not changed.

b) Master reads slave immediately after first byte.

At the moment of the first acknowledge, the master transmitter becomes a master receiver and the slave receiver becomes a slave transmitter. This acknowledge is still generated by the slave.

The STOP condition is generated by the master.

c) Combined formats.

During a change of direction within a transfer, the START condition and the slave address are both repeated, but with the R/W bit reversed.

#### NOTES:

- Combined formats can be used, for example, to control a serial memory. During the first data byte, the internal memory location has to be written. After the START condition is repeated, data can be transferred.

- 2) All decisions on auto-increment or decrement of previously accessed memory locations etc. are taken by the designer of the IC.

- 3) Each byte is followed by an acknowledge as indicated by the A blocks in the sequence.

- 4) I<sup>2</sup>C-bus compatible ICs must reset their bus logic on receipt of a START condition such that they all anticipate the sending of a slave address.

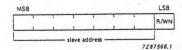

Fig.10 The first byte after the start procedure

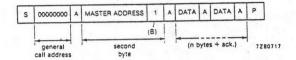

## 8.0 Addressing

The addressing procedure for the I<sup>2</sup>C-bus is such that the first byte after the START condition determines which slave will be selected by the master. Usually, this first byte follows that start procedure. The exception is the 'general call' address which can address all ICs. When this address is used, all ICs should, in theory, respond with an acknowledge. However, ICs can be made to ignore this address. The second byte of the general call address then defines the action to be taken.

### 8.1 Definition of bits in the first byte

The first seven bits of the first byte make up the slave address (Fig. 10). The eighth bit is the LSB (least significant bit). It determines the direction of the message. A 'zero' in the least significant position of the first byte means that the master will write information to a selected slave. A 'one' in this position means that the master will read information from the slave.

When an address is sent, each IC in a system compares the first 7 bits after the START condition with its address. If they match, the IC considers itself addressed by the master as a slave receiver or slave transmitter, depending on the R/W bit.

A slave address can be made-up of a fixed and a programmable part. Since it's likely that there will be several identical ICs in a system, the programmable part of the slave address enables the maximum possible number of such ICs to be connected to the I<sup>2</sup>C-bus. The number of programmable address bits of an IC depends on the number of pins available. For example, if an IC has 4 fixed and 3 programmable address bits, a total of 8 identical ICs can be connected to the same bus.

The I<sup>2</sup>C-bus committee coordinates allocation of I<sup>2</sup>C addresses. The bit combination 1111XXX of the slave address is reserved for future extension purposes. Address 1111111 is reserved as the extension address. This means that the addressing procedure will be continued in the next byte(s). ICs that don't use the extended addressing don't react on reception of this byte. The seven other possibilities in group 1111 will also only be used for extension purposes but are not yet allocated. Combination 0000XXX has been defined as a special group. The following addresses have been allocated (also see notes on next page):

| first by         | te                                          |                  |

|------------------|---------------------------------------------|------------------|

| SLAVE<br>ADDRESS | R∕₩                                         |                  |

| 0000 000         | 0 general call address                      |                  |

| 0000 000         | 1 start byte                                |                  |

|                  |                                             | see              |

| 0000 001         | X CBUS address                              | NOTES on page 15 |

| 0000 010         | X Address reserved for different bus format |                  |

| 0000 011         | X)                                          |                  |

| 0000 100         | X                                           |                  |

| 0000 101         | X to be defined                             |                  |

| 0000 110         | X                                           |                  |

| 0000 111         | x )                                         |                  |

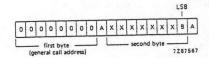

Fig.11 General call address format

Fig.12 Sequence of a programming master

#### NOTES:

- 1) No IC is allowed to acknowledge at the reception of the START byte.

- 2) The CBUS address has been reserved to enable the inter-mixing of CBUS compatible and I<sup>2</sup>C-bus compatible ICs in the same system. I<sup>2</sup>C-bus compatible ICs are not allowed to respond on reception of this address.

- 3) The address reserved for a different bus format is included to enable I<sup>2</sup>C and other protocols to be mixed. Only I<sup>2</sup>C-bus compatible ICs that can work with such formats and protocols are allowed to respond to this address.

## 8.1.1 General call address

The general call address should be used to address every IC connected to the I<sup>2</sup>C-bus. However, if an IC doesn't need any of the data supplied within the general call structure, it can ignore this address by not acknowledging. If an IC does require data from a general call address, it will acknowledge this address and behave as a slave receiver. The second and following bytes will be acknowledged by every slave receiver capable of handling this data. A slave which cannot process one of these bytes must ignore it by not acknowledging. The meaning of the general call address is always specified in the second byte (Fig.11).

There are two cases to consider:

- · When the least significant bit B is a 'zero'.

- · When the least significant bit B is a 'one'.

When B is a 'zero'; the second byte has the following definition:

- 00000110 (H'06') Reset and write programmable part of slave address by software and hardware. On receiving this 2-byte sequence, all ICs designed to respond to the general call address will reset and take in the programmable part of their address. Precautions have to be taken to ensure that an IC is not pulling down the SDA or SCL line after applying the supply voltage, since these low levels would block the bus.

- 00000010 (H'02') Write slave address by software only. All ICs which obtain the programmable part of their address by software (and which have been designed to respond to the general call address) will enter a mode in which they can be programmed. The IC will not reset.

An example of a data transfer of a programming master is shown in Fig.12 (ABCD represents the fixed part of the address).

- 00000100 (H'04') Write slave address by hardware only. All ICs which define the programmable part of their address by hardware (and which respond to the general call address) will latch this programmable part at the reception of this two byte sequence. The IC will not reset.

- 00000000 (H'00') This code is not allowed to be used as the second byte.

Sequences of programming procedure are published in the appropriate IC data sheets.

The remaining codes have not been fixed and ICs must ignore them.

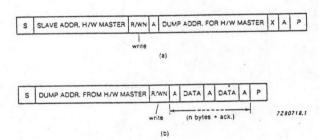

Fig.13 Data transfer from a hardware master transmitter

Fig.14 Data transfer by a hardware transmitter capable of dumping data directly to slave ICs

- (a) Configuring master sends dump address to hardware master

- (b) Hardware master dumps data to selected slave

Fig.15 Start byte procedure

When B is a 'one'; the 2-byte sequence is a 'hardware general call'. This means that the sequence is transmitted by a hardware master IC, such as a keyboard scanner, which cannot be programmed to transmit a desired slave address. Since a hardware master doesn't know in advance to which IC the message has to be transferred, it can only generate this hardware general call and its own address - identifying itself to the system (Fig. 13).

The seven bits remaining in the second byte contain the address of the hardware master. This address is recognised by an intelligent IC, such as a microcomputer, connected to the bus which will then direct the information from the hardware master. If the hardware master can also act as a slave, the slave address is

identical to the master address.

In some systems, an alternative could be that the hardware master transmitter is set in the slave receiver mode after the system reset. In this way, a system configuring master can tell the hardware master transmitter (which is now in slave receiver mode) to which address data must be sent (Fig. 14). After this programming procedure, the hardware master remains in the master transmitter mode.

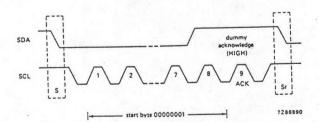

### 8.1.2 start byte

Microcomputers can be connected to the I2C-bus in two ways. A microcomputer with an on-chip hardware I<sup>2</sup>C-bus interface can be programmed to be only interrupted by requests from the bus. When the IC doesn't have such an interface, it must constantly monitor the bus via software. Obviously, the more times the microcomputer monitors, or polls, the bus the less time it can spend carrying out its intended function. There is therefore a speed difference between fast hardware ICs and a relatively slow microcomputer which relies on software polling.

In this case, data transfer can be preceded by a start procedure which is much

longer than normal (Fig. 15). The start procedure consists of:

- a) A START condition S

- b) A start byte 00000001

- c) An acknowledge clock pulse

- d) A repeated START condition Sr

After the START condition S has been transmitted by a master which requires bus access, the start byte (00000001) is transmitted. Another microcomputer can therefore sample the SDA line at a low sampling rate until one of the seven zeros in the start byte is detected. After detection of this LOW level on the SDA line, the microcomputer can switch to a higher sampling rate to find the repeated START condition Sr which is then used for synchronization.

A hardware receiver will reset on receipt of the repeated START condition Sr

and will therefore ignore the start byte.

An acknowledge-related clock pulse is generated after the start byte. This is present only to conform with the byte handling format used on the bus. No IC is allowed to acknowledge the start byte.

Fig.16 Data format of transmissions with CBUS receiver/transmitter

Fig.17 Fixed input level ICs connected to the  ${\rm I}^2{\rm C}$ -bus

Fig.18 ICs with a wide range of supply voltages connected to the  ${\rm I}^2{\rm C}$ -bus

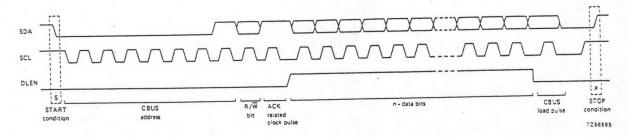

### 8.1.3 CBUS compatibility

Existing CBUS receivers can be connected to the I<sup>2</sup>C-bus. However, in this case, a third line called DLEN has to be connected and the acknowledge bit omitted. Normally, I<sup>2</sup>C transmissions are sequences of 8-bit bytes; CBUS compatible ICs have different formats however.

In a mixed bus structure, I<sup>2</sup>C-bus compatible ICs are not allowed to respond to the CBUS message. For this reason, a special CBUS address (0000001X) to which no I<sup>2</sup>C-bus compatible IC will respond, has been reserved. After transmission of the CBUS address, the DLEN line can be made active and transmission, according to the CBUS format, can be performed (Fig.16). After the STOP condition, all ICs are again ready to accept data.

Master transmitters are allowed to generate CBUS formats after having sent the CBUS address. Such a transmission is terminated by a STOP condition, recognised by all ICs. In the 'low speed' mode (see Section 11.0), full 8-bit bytes must always be transmitted and the timing of the DLEN signal adapted.

NOTE: If the CBUS configuration is known, and expansion with CBUS compatible ICs isn't foreseen, the designer is allowed to adapt the hold time to the specific requirements of IC(s) used.

# 9.0 Electrical specifications of inputs and outputs of I2C interfaces

The  $I^2C$ -bus allows communication between ICs fabricated in different technologies which might also operate from different supply voltages. For interfaces with fixed input levels, operating on a supply voltage of 5 V  $\pm$  10%, the following levels have been defined:

$V_{IL max} = 1.5 \text{ V (maximum input LOW voltage)}$

$V_{IH min} = 3.0 V (minimum input HIGH voltage)$

Interfaces in ICs operating from a fixed supply voltage other than 5 V (e.g.  $I^2L$  ICs), must also have these input levels of 1.5 V and 3.0 V for  $V_{IL}$  and  $V_{IH}$  respectively.

For ICs capable of operating from a wide range of supply voltages (e.g. CMOS ICs), the following levels have been defined:

$V_{IL \text{ max}} = 0.3 V_{DD}$  (maximum input LOW voltage)

$V_{IH min} = 0.7 V_{DD}$  (minimum input HIGH voltage)

The maximum output LOW level for both groups is:

$V_{OL max} = 0.4 V at 3 mA sink current.$

The maximum LOW level input current at  $V_{OL\ max}$  of both the SDA and SCL pin of an I<sup>2</sup>C-bus compatible IC is -10  $\mu$ A, including the leakage current of a possible output stage.

The maximum HIGH level input current at 90%  $V_{DD}$  for both the SDA and SCL pin of an I<sup>2</sup>C-bus compatible IC is 10  $\mu$ A, including the leakage current of a possible output stage.

The maximum capacitance of both the SDA and SCL pin of an I<sup>2</sup>C-bus compatible IC is 10 pF.

$I^2C$  interfaces with fixed input levels can each have their own power supply of 5 V  $\pm$  10%. Pull-up resistors can be connected to any supply (Fig.17). However,  $I^2C$

Fig.19 Interfaces with input levels related to  $V_{\mbox{DD}}$  mixed with fixed input level interfaces on the  $I^2C$ -bus

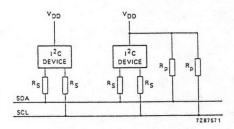

Fig.20 Series resistors ( $R_s$ ) for protection against high-voltage spikes

interfaces with input levels related to V<sub>DD</sub> must have one common supply line to which the pull-up resistor is also connected (Fig. 18).

When ICs having interfaces with fixed input levels are mixed with ICs which have interfaces with input levels related to  $V_{DD}$ , the latter ICs must be connected to one common supply line of 5 V  $\pm$  10% and must have pull-up resistors connected to their SDA and SCL pins as shown in Fig.19.

Input levels are defined in such a way that:

- 1) The noise margin on the LOW level is 0.1  $\rm V_{\rm DD}$

- 2) The noise margin on the HIGH level is 0.2  $V_{\rm DD}$ .

- 3) Series resistors ( $R_s$ ) up to 300  $\Omega$  can be used for protection against high voltage spikes on the SDA and SCL line due to flash-over of a TV picture tube, for example (Fig.20).

The maximum bus capacitance per wire is 400 pF. This includes the capacitance of the wire itself and the capacitance of the pins connected to it.

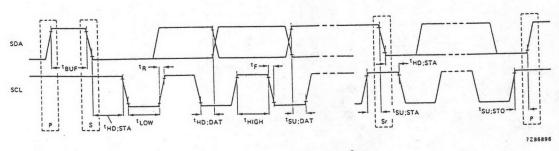

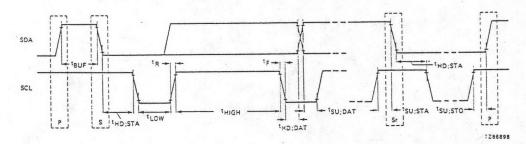

10.0 Timing

The clock on the  $I^2$ C-bus has a minimum LOW period of 4.7  $\mu$ s and a minimum HIGH period of 4  $\mu$ s. Masters in this mode can generate a bus clock with a frequency up to 100 kHz.

All ICs connected to the bus must be able to follow transfers with frequencies up to 100 kHz, either by being able to transmit or receive at that speed or by applying the clock synchronization procedure which will force the master into a wait state and stretch the LOW periods. Of course, in the latter case the frequency is reduced.

Figure 21 shows the timing requirements in detail, a description of the abbreviations used is shown in the following Table. All timing references are at  $V_{\rm IL\ max}$  and  $V_{\rm IH\ min}$ .

|                     | min.                                                  | max.                                                                                        | units                                                                                                                                                                                                                                                     |

|---------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fscl                | 0                                                     | 100                                                                                         | kHz                                                                                                                                                                                                                                                       |

| <sup>t</sup> BUF    | 4.7                                                   | ·                                                                                           | μς                                                                                                                                                                                                                                                        |

| tHD;STA             | 4.0                                                   |                                                                                             | μs                                                                                                                                                                                                                                                        |

|                     |                                                       |                                                                                             |                                                                                                                                                                                                                                                           |

| Low                 | 4.7                                                   |                                                                                             | μѕ                                                                                                                                                                                                                                                        |

| <sup>t</sup> нісн   | 4.0                                                   | •                                                                                           | μз                                                                                                                                                                                                                                                        |

| tsu;sta             | 4.7                                                   |                                                                                             | με                                                                                                                                                                                                                                                        |

| tHD;DAT             | 5                                                     |                                                                                             | με                                                                                                                                                                                                                                                        |

|                     | 0*                                                    | ·                                                                                           | hz                                                                                                                                                                                                                                                        |

| tsu;dat             | 250                                                   | • •                                                                                         | ns                                                                                                                                                                                                                                                        |

| <sup>t</sup> R      | •                                                     | 1                                                                                           | μs                                                                                                                                                                                                                                                        |

| t <sub>F</sub>      |                                                       | 300                                                                                         | ns                                                                                                                                                                                                                                                        |

| t <sub>SU;STC</sub> | 4.7                                                   | •                                                                                           | μѕ                                                                                                                                                                                                                                                        |

|                     | thd;sta thd;sta thd;sta thd;dat tsu;sta thd;dat tr tr | fscl 0 fbuf 4.7 fhD;STA 4.0 flow 4.7 fhIGH 4.0 fsu;STA 4.7 fhD;DAT 5 0* fsu;DAT 250 fR - fr | f <sub>SCL</sub> 0 100  t <sub>BUF</sub> 4.7 -  t <sub>HD;STA</sub> 4.0 -  t <sub>LOW</sub> 4.7 -  t <sub>HIGH</sub> 4.0 -  t <sub>SU;STA</sub> 4.7 -  t <sub>HD;DAT</sub> 5 -  0* -  t <sub>SU;DAT</sub> 250 -  t <sub>R</sub> - 1  t <sub>F</sub> - 300 |

All values referred to  $V_{\mbox{\scriptsize IL}}$  and  $V_{\mbox{\scriptsize IL}}$  levels (see section 9.0).

Fig.21 Timing requirements for the I<sup>2</sup>C-bus

<sup>\*</sup> Note that a transmitter must internally provide at least a hold time to bridge the undefined region (max. 300 ns) of the falling edge of SCL.

# 11.0 'Low speed' mode

As explained in section 8.1.2, there is a difference in speed on the I<sup>2</sup>C-bus between fast hardware interfaces and a relatively slow microcomputer which relies on software polling. For this reason a 'low speed' mode is available on the I<sup>2</sup>C-bus to allow these microcomputers to poll the bus less often.

## 11.1 START and STOP conditions

In the 'low speed' mode, data transfer is preceded by the start procedure of section 8.1.2.

## 11.2 Data format and timing

The bus clock in this mode has a LOW period of 130  $\mu s \pm 25 \mu s$  and a HIGH period of 390  $\mu s \pm 25 \mu s$ , resulting in a clock frequency of about 2 kHz. This clock duty cycle allows for more efficient use of microcomputers without an on-chip hardware I<sup>2</sup>C-bus interface. Also in this mode, data transfer with acknowledge is obligatory. the maximum number of bytes transferred is unlimited (Fig.22).

In this mode, a transfer cannot be terminated during the transmission of a byte.

| Clock:                                                                                | $t_{LOW} = 130 \mu s \pm 25 \mu s$ $t_{HIGH} = 390 \mu s \pm 25 \mu s$ |

|---------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Outy cycle:                                                                           | 1:3 LOW to HIGH (Duty cycle of clock generator)                        |

| Start byte:                                                                           | 0000 0001                                                              |

| Max. number of bytes:                                                                 | unrestricted                                                           |

| oremature termination: of transfer: acknowledge clock bit: acknowledgement of slaves: | not allowed always provided obligatory                                 |

The bus is considered to be busy after the first START condition. It is considered to be free again one minimum clock LOW period (105  $\mu$ s) after detection of the STOP condition. Figure 23 shows the timing requirements in detail and the following Table explains the abbreviations.

Fig.22 Data transfer in the 'low speed' mode

Fig.23 Timing in the 'low speed' mode

| parameter                                                                            | symbol              | min. | max. | units |  |

|--------------------------------------------------------------------------------------|---------------------|------|------|-------|--|

| Time the bus must be free before a new transmission can start                        | BUF                 | 105  | •    | με    |  |

| Hold time START condition. After this seriod the first clock pulse is generated      | tHD;STA             | 365  |      | με    |  |

| Hold time (repeated START condition only)                                            | tHD;STA             | 210  |      | μς    |  |

| LOW period of the clock                                                              | Low                 | 105  | 155  | μς    |  |

| HIGH period of the clock                                                             | HIGH                | 365  | 415  | μς    |  |

| Set up time for START condition<br>(Only relevant for a repeated START<br>condition) | <sup>t</sup> SU;STA | 105  | 155  | μѕ    |  |

| Hold time DATA for CBUS compatible masters (see                                      | tHD;DAT             | 5    |      | μѕ    |  |

| also NOTE, Section 8.1.3) for I <sup>2</sup> C ICs                                   |                     | 0*   |      | μς    |  |

| Set-up time DATA                                                                     | tsu;dat             | 250  | •    | ns    |  |

| Rise time of both SDA and SCL lines                                                  | 'n                  | •    | 1    | μs    |  |

| Fall time of both SDA and SCL lines                                                  | <sup>t</sup> F      | •    | 300  | ns    |  |

| Set-up time for STOP condition                                                       | tsu;sto             | 105  | 155  | hra   |  |

All values referred to  $V_{\hbox{IH}}$  and  $V_{\hbox{IL}}$  levels (see section 9.0).

Note that a transmitter must internally provide at least a hold time to bridge the undefined region (max. 300 ns) of the falling edge of SCL.

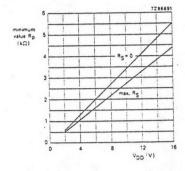

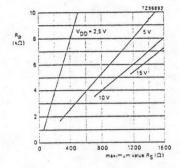

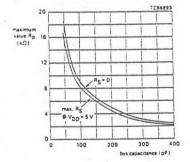

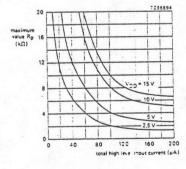

# Appendix A - Values of resistors R<sub>p</sub> and R<sub>s</sub> in Fig.20

In an I<sup>2</sup>C-bus system these values depend on the following parameters:

- 1) Supply voltage

- 2) Bus capacitance

- 3) Number of connected ICs (input current + leakage current)

- 1) The supply voltage limits the minimum value of resistor  $R_p$  due to the specified minimum sink current of 3 mA at  $V_{OLmax} = 0.4$  V for the output stages.  $V_{DD}$  as a function of  $R_p$  min is shown in a graph on the facing page. The desired noise margin of 10% 0f  $V_{DD}$  for the LOW level limits the maximum value of  $R_s$ .  $R_s$  max as a function of  $R_p$  is shown in another graph on the facing page.

- 2) The bus capacitance is the total capacitance of wire, connections and pins. This capacitance limits the maximum value of R<sub>p</sub> due to the specified rise time of 1 µsec. A graph on the facing page shows R<sub>p max</sub> as a function of bus capacitance.

- 3) The maximum HIGH level input current of each input/output connection has a specified maximum value of 10  $\mu$ A. Due to the desired noise margin of 20% of  $V_{DD}$  for the HIGH level, this input current limits the maximum value of  $R_p$ . This limit depends on  $V_{DD}$ . The total HIGH level input current is shown as a function of  $R_p$  max in a graph on the facing page.

## Appendix B - Note to section 6.2

Special attention must be paid if, during a serial transfer, the arbitration procedure is still in progress at the moment when a repeated START condition or a STOP condition is transmitted to the I<sup>2</sup>C-bus. If it's possible for such a situation to occur, the masters involved must send this repeated START condition or STOP condition at the same position in the format frame. In other words, arbitration isn't allowed between:

- a repeated START condition and a data bit,

- a STOP condition and a data bit,

- a repeated START condition and a STOP condition.

ภาคผนวก ข. Data Sheet

SAA5231

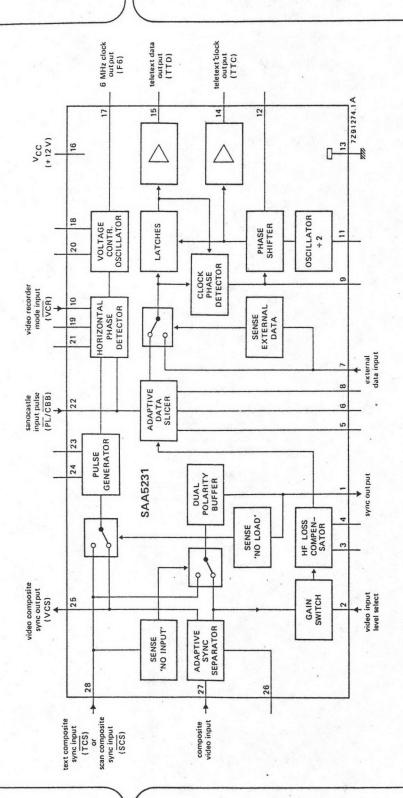

### TELETEXT VIDEO PROCESSOR

#### GENERAL DESCRIPTION

The SAA5231 is a bipolar integrated circuit intended as a successor to the SAA5030. It extracts Teletext Data from the video signal, regenerates Teletext Clock and synchronizes the text display to the television syncs. The integrated circuit is intended to work in conjunction with CCT (Computer Controlled Teletext), EUROM or other compatible devices.

#### **Features**

- Adaptive data slicer

- Data clock regenerator

- Adaptive sync separator, horizontal phase detector and 6 MHz VCO forming display phase locked loop (PLL)

#### QUICK REFERENCE DATA

|                                                               |                         | and the second second second second |            |

|---------------------------------------------------------------|-------------------------|-------------------------------------|------------|

| Supply voltage (pin 16)                                       | V <sub>CC</sub>         | typ.                                | 12 V       |

| Supply current (pin 16)                                       | Icc                     | typ.                                | 70 mA      |

| Video input amplitude (pin 27) (peak-to-peak value) pin 2 LOW | V <sub>27-13(p-p)</sub> | typ.                                | 1 V        |

| pin 2 HIGH                                                    | V <sub>27-13(p-p)</sub> | typ.                                | 2,5 V      |

| Storage temperature range                                     | T <sub>stg</sub>        |                                     | + 125 °C   |

| Operating ambient temperature range                           | T <sub>amb</sub>        | 0 1                                 | to + 70 °C |

|                                                               |                         |                                     |            |

PACKAGE OUTLINE

28-lead dual in-line; plastic (SOT117).

SAA5231

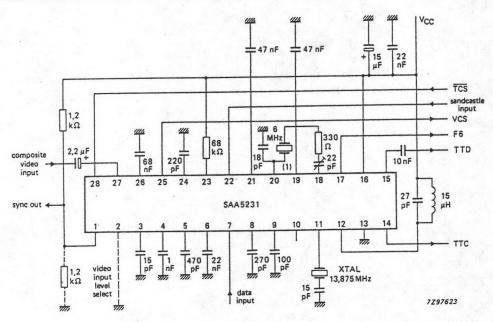

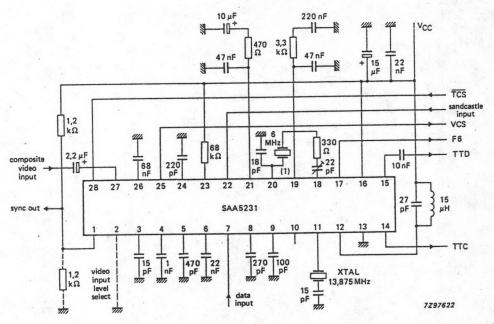

Fig. 1 Block diagram.

Teletext video processor

SAA5231

#### PINNING

Fig. 2 Pinning diagram.

#### **RATINGS**

| RATINGS                                               |                      |        |          |     |

|-------------------------------------------------------|----------------------|--------|----------|-----|

| Limiting values in accordance with the Absolute Maxim | num System (IEC 134) |        | e malend | 519 |

| Supply voltage (pin 16)                               | Vcc                  | max.   | 13,2     |     |

| Storage temperature range                             | T <sub>stq</sub>     | -20 to | + 125    | oC  |

| Operating ambient temperature                         | T <sub>amb</sub>     | 0 t    | 0 + 70   | oC  |

# SAA5231

#### CHARACTERISTICS

$V_{CC}$  = 12 V;  $T_{amb}$  = 25 °C with external components as shown in application circuits unless otherwise stated.

| parameter •                                                | symbol                   | min. | typ.  | max. | unit |

|------------------------------------------------------------|--------------------------|------|-------|------|------|

| Supply (pin 16)                                            |                          |      |       |      |      |

| Supply voltage                                             | Vcc                      | 10,8 | 12,0  | 13,2 | ٧    |

| Supply current                                             | Icc                      | 50   | 70    | 105  | mA   |

| Video input and sync separator                             |                          |      |       |      |      |

| Video input amplitude (sync to white) (peak-to-peak value) |                          |      |       |      |      |

| video input select level LOW (pin 2)                       | V <sub>27-13(p-p)</sub>  | 0,7  | 1     | 1,4  | V    |

| video input select level HIGH (pin 2)                      | V <sub>27</sub> -13(p-p) | 1,75 | 2,5   | 3,5  | V    |

| Source impedance                                           | Z <sub>s</sub>           | -    | -     | 250  | Ω    |

| Sync amplitude (peak-to-peak value)                        | V <sub>27</sub> -13(p-p) | 0,1  | -     | 1    | ٧    |

| Video input level select                                   |                          |      |       |      |      |

| Input voltage LOW                                          | V <sub>2-13</sub>        | 0    | -     | 8,0  | ٧    |

| Input voltage HIGH                                         | V <sub>2-13</sub>        | 2,0  | -     | 5,5  | ٧    |

| Input current LOW                                          | 12                       | 0    | -     | -150 | μΑ   |

| Input current HIGH                                         | 12                       | .0   | -     | 1    | mA   |

| Text composite sync input (TCS)                            |                          |      |       |      |      |

| Input voltage LOW                                          | V <sub>28-13</sub>       | 0    | -     | 0,8  | V    |

| Input voltage HIGH                                         | V <sub>28-13</sub>       | 2,0  | -     | 7,0  | ٧    |

| Scan composite sync input (SCS)                            |                          |      |       |      |      |

| Input voltage LOW                                          | V <sub>28-13</sub>       | 0    | _     | 1,5  | V    |

| Input voltage HIGH                                         | V <sub>28-13</sub>       | 3,5  | -     | 7,0  | ٧    |

| Select video sync from pin 1                               |                          |      | x - 3 |      |      |

| Input current (pin 28)                                     |                          |      |       |      |      |

| at V <sub>28</sub> = 0 to 7 V                              | 128                      | -40  | -70   | -100 | μΑ   |

| at V <sub>28</sub> = 10 V to V <sub>CC</sub>               | 128                      | -5   | -     | + 5  | μΑ   |

| Video composite sync output (VCS)                          |                          |      | 200   |      |      |

| Output voltage LOW                                         | V <sub>25-13</sub>       | 0    | -     | 0,4  | V    |

| Output voltage HIGH                                        | V <sub>25-13</sub>       | 2,4  | -     | 5,5  | V    |

| D.C. output current LOW                                    | 1 <sub>25</sub>          | -    | -     | 0,5  | mA   |

| D.C. output current HIGH                                   | 1 <sub>25</sub>          | -    | -     | -1,5 | mA   |

| Sync separator delay time                                  | t <sub>d</sub>           | 0,25 | 0,35  | 0,40 | μs   |

## Teletext video processor

| parameter                                | symbol                          | min. | typ.   | max. | unit |

|------------------------------------------|---------------------------------|------|--------|------|------|

| Dual polarity buffer output              |                                 |      |        |      |      |

| TCS amplitude                            |                                 |      |        |      |      |

| (peak-to-peak value)                     | V <sub>1-13(p-p)</sub>          | 0,20 | 0,45   | 0,65 | V    |

| Video sync amplitude                     |                                 |      |        | 1    | V    |

| (peak-to-peak value)                     | V <sub>1-13(p-p)</sub>          | -    | T- 447 | +3   | mA   |

| Output current                           | 11                              | -3   | _      | +3   | mA   |

| D.C. output voltage                      |                                 |      |        |      | .,   |

| R <sub>L</sub> to ground (0 V)           | V <sub>1-13</sub>               | 1,0  | 1,4    | 2,0  | V    |

| R <sub>L</sub> to V <sub>CC</sub> (12 V) | V <sub>1-13</sub>               | 9,0  | 10,1   | 11,0 | V    |

| Sandcastle input pulse (PL/CBB)          |                                 |      |        |      |      |

| Phase lock pulse (PL)                    |                                 |      |        |      |      |

| PL on (LOW)                              | V <sub>22-13</sub>              | 0    | - 34   | 3    | V    |

| PL off (HIGH)                            | V <sub>22-13</sub>              | 3,9  | -      | 5,5  | V    |

| Blanking pulse (CBB)                     |                                 |      |        |      |      |

| CBB on (LOW)                             | V <sub>22-13</sub>              | 0    | -      | 0,5  | V    |

| CBB off (HIGH)                           | V <sub>22-13</sub>              | 1,0  | -      | 5,5  | V    |

| Input current                            | 122                             | -10  | -      | + 10 | μΑ   |

| Phase locked loop (PLL)                  |                                 |      |        |      |      |

| Phase detector timing                    |                                 |      |        |      |      |

| Pulse duration                           |                                 |      |        |      |      |

| using composite video                    | tp                              | 2,0  | 2,4    | 2,8  | μѕ   |

| using scan composite sync                | tp                              | 3,0  | 3,5    | 4,0  | μs   |

| time PL must be LOW                      |                                 | 100  |        |      | μs   |

| to make VCO run-free                     | tL                              | 100  | - 0    |      | μς   |

| 6 MHz clock output (F6)                  |                                 |      |        |      | 1    |

| A.C. output voltage                      |                                 |      | 1      | 2    | V    |

| (peak-to-peak value)                     | V <sub>17-13(p-p)</sub>         | 1    | 2      | 3    | V    |

| A.C. and d.c. output voltage range       | V <sub>17-13(max)</sub>         | 4    | -      | 8,5  | 100  |

| Rise and fall time                       | t <sub>r</sub> ; t <sub>f</sub> | 20   | -      | 40   | ns   |

| Load capacitance                         | C <sub>17</sub> -13             | -    | -      | 40   | pF   |

| Video recorder mode input (VCR)          |                                 |      |        |      |      |

| VCR-mode on (LOW)                        | V <sub>10-13</sub>              | 0    | -      | 0,8  | V    |

| VCR-mode off (HIGH)                      | V <sub>10-13</sub>              | 2,0  | -      | Vcc  | V    |

| Input current                            | 110                             | -10  | -      | +10  | μА   |

| parameter                                            | symbol                  | min. | typ. | max. | unit |

|------------------------------------------------------|-------------------------|------|------|------|------|

| Data slicer                                          |                         |      |      |      |      |

| Data amplitude of video input (pin 27)               |                         |      |      |      |      |

| video input level select LOW (pin 2)                 | V <sub>27-13</sub>      | 0,30 | 0,46 | 0,70 | V    |

| video input level select HIGH (pin 2)                | V <sub>27-13</sub>      | 0,75 | 1,15 | 1,75 | V    |

| Teletext clock output                                |                         |      |      |      |      |

| A.C. output voltage (peak-to-peak value)             | V <sub>14-13(p-p)</sub> | 2,5  | 3,5  | 4,5  | V    |

| D.C. output voltage (centre)                         | V14-13                  | 3,0  | 4,0  | 5,0  | V    |

| Load capacitance                                     | CL                      | -    | -    | 40   | pF   |

| Rise and fall times                                  | tr; tf                  | 20   | 30   | 45   | ns   |

| Delay of falling edge relative to other edges of TTD | <sup>t</sup> d          | -20  | 0    | + 20 | ns   |

| Teletext data output                                 |                         |      |      |      |      |

| A.C. output voltage                                  |                         | 0.5  | 2.5  | 4.5  | V    |

| (peak-to-peak value)                                 | V <sub>15-13(p-p)</sub> | 2,5  | 3,5  | 4,5  |      |

| D.C. output voltage (centre)                         | V <sub>15-13</sub>      | 3,0  | 4,0  | 5,0  | V    |

| Load capacitance                                     | CL                      | -    | -    | 40   | pF   |

| Rise and fall times                                  | tr; tf                  | 20   | 30   | 45   | ns   |

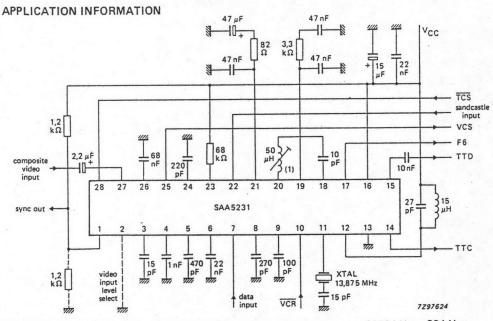

(1) Coil: 50  $\mu$ H at 1 kHz, C<sub>0</sub> = 4 pF. Adjust the free-running frequency to 6000 kHz  $\pm$  30 kHz. Fig. 3a Application circuit using L/C circuit in PLL.

(1) Quartz crystal e.g. catalogue number 4322 143 04101. Adjust the free-running frequency to 6000,2 kHz ± 0,2 kHz.

Fig. 3b Application circuit using quartz crystal in PLL.

(1) Ceramic resonator e.g. Kyocera KBR 6,0 M. Adjust the free-running frequency to 6010 kHz  $\pm$  5 kHz.

Fig. 3c Application circuit using ceramic resonator in PLL.

579

#### Component specifications

Specifications of some external components in Figs 3a, 3b and 3c.

#### Quartz crystal 13,875 MHz; Figs 3a, 3b and 3c

Load resonance frequency (f) 13,875 MHz; adjustment tolerance ± 40·10-6

Load capacitance (CL) 20 pF

Temperature range (T) -20 to +70 °C; frequency tolerance maximum ± 30-10-6

Resonance resistance (R<sub>r</sub>) typical 10  $\Omega$  maximum 60  $\Omega$

Motional capacitance (C<sub>1</sub>) typical 19 fF

Static parallel capacitance (Co) typical 5 pF

#### Fixed inductance Figs 3a, 3b and 3c

Inductance (L) 15  $\mu$ H ± 20%

Quality factor (Q) minimum 20

#### Variable inductance Fig. 3a

Inductance (L) 50 µH at 1 kHz

Static parallel capacitance (Co) typical 4 pF

#### Quartz crystal Fig. 3b

Preferred type 4322 143 04101

Load resonance frequency (f) 6 MHz; adjustment tolerance ± 40·10-6

Load capacitance (CL) 20 pF

Temperature range (T) -20 to +70 °C; frequency tolerance ± 30·10-6

Resonance resistance (R<sub>r</sub>)  $60 \Omega$

Motional capacitance (C1) typical 28 fF

Static parallel capacitance (Co) typical 7 pF

#### Ceramic resonator; Fig. 3c

Preferred type KBR 6,0 M, Kyocera

Load resonance frequency (f) 6 MHz; adjustment tolerance ± 0,5%

Load capacitance (C<sub>L</sub>) 20 pF

Temperature range (T) -20 to +70 °C; frequency tolerance maximum ± 0,3%

Resonance resistance (R<sub>r</sub>) typical 6  $\Omega$

Motional capacitance (C<sub>1</sub>) typical 9 pF

Static parallel capacitance (Co) typical 60 pF

Ageing (10 years) f maximum ± 0,3%

Teletext video processor

SAA5231

The function is quoted against the corresponding pin number.

#### 1. Synch output to TV

Output with dual polarity buffer, a load resistor to 0 V or + 12 V selects positive-going or negative-going syncs.

#### 2. Video input level select

When this pin is LOW a 1 V video input level is selected. When the pin is not connected it floats HIGH selecting a 2,5 V video input level.

#### 3 HF filter

The video signal for the h.f.-loss compensator is filtered by a 15 pF capacitor connected to this pin.

#### 4. Store h.f.

The h.f. amplitude is stored by a 1 nF capacitor connected to this pin.

#### 5. Store amplitude

The amplitude for the adaptive data slicer is stored by a 470 pF capacitor connected to this pin.

#### 6 Store zero level

The zero level for the adaptive data slicer is stored by a 22 nF capacitor connected to this pin.

#### 7. External data input

Current input for sliced teletext data from external device. Active HIGH level (current), low impedance input.

#### 8. Data timing

A 270 pF capacitor is connected to this pin for timing of the adaptive data slicer.

#### 9. Store phase

The output signal from the clock phase detector is stored by a 100 pF capacitor connected to this pin.

### 10. Video tape recorder mode (VCR)

Signal input to command PLL into short time constant mode. Not used in application circuit Fig. 3b or Fig. 3c.

#### 11. Crystal

A 13,875 MHz crystal, 2 x data rate, connected in series with a 15 pF capacitor is applied via this pin to the oscillator and divide-by-two to provide the 6,9375 MHz clock signal.

#### 12. Clock filter

A filter for the 6,9375 MHz clock signal is connected to this pin.

### 13. Ground (0 V)

#### 14. Teletext clock output (TTC)

Clock output for CCT (Computer Controlled Teletext).

## APPLICATION INFORMATION (continued)

#### 15. Teletext data output (TTD)

Data output for CCT.

#### 16. Supply voltage V<sub>CC</sub> (+ 12 V typ.)

#### 17. Clock output (F6)

6 MHz clock output for timing and sandcastle generation in CCT.

#### 18. Oscillator output (6 MHz)

A series resonant circuit is connected between this pin and pin 20 to control the nominal frequency of the VCO.

#### 19. Filter 2

A filter with a short time constant is connected to this pin for the horizontal phase detector. It is used in the video recorder mode and while the loop is locking up.

#### 20. Oscillator input (6 MHz)

See pin 18.

#### 21, Filter 1

A filter with a long time constant is connected to this pin for the horizontal phase detector.

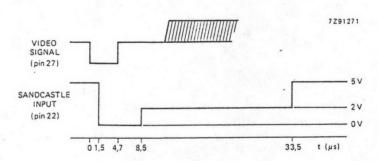

## 22. Sandcastle input pulse (PL/CBB)

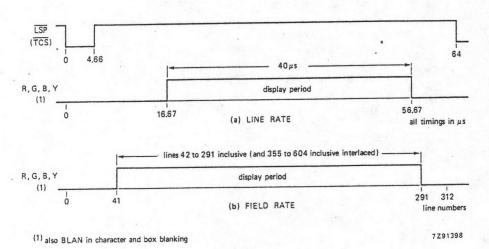

This input accepts a sandcastle waveform, which is formed from PL and CBB from the CCT. Signal timing is shown in Fig. 4.

#### 23. Pulse timing resistor

The current for the pulse generator is defined by a  $68\,\mathrm{k}\Omega$  resistor connected to this pin.

#### 24. Pulse timing capacitor

The timing of the pulse generator is determined by a 220 pF capacitor connected to this pin.

## 25. Video composite sync output (VCS)

This output signal is for CCT.

#### 26. Black level

The black level for the adaptive sync separator is stored by a 68 nF capacitor connected to this pin.

## 27. Composite video input (CVS)

The composite video signal is input via a 2,2  $\mu\text{F}$  clamping capacitor to the adaptive sync separator.

## 28. Text composite sync input (TCS)/Scan composite sync input (SCS)

$\overline{TCS}$  is input from CCT or  $\overline{SCS}$  from external sync circuit.  $\overline{SCS}$  is expected when there is no load resistor at pin 1. If pin 28 is not connected the sync output on pin 1 will be the composite video input at pin 27, internally buffered.

Fig. 4 Sandcastle waveform and timing.

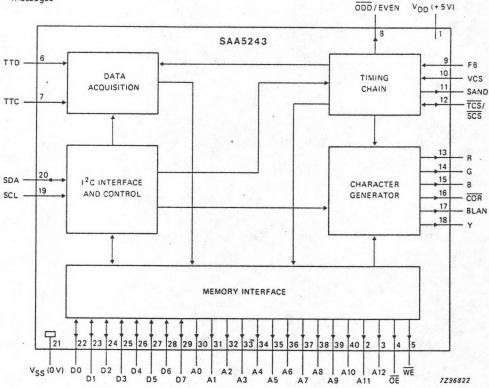

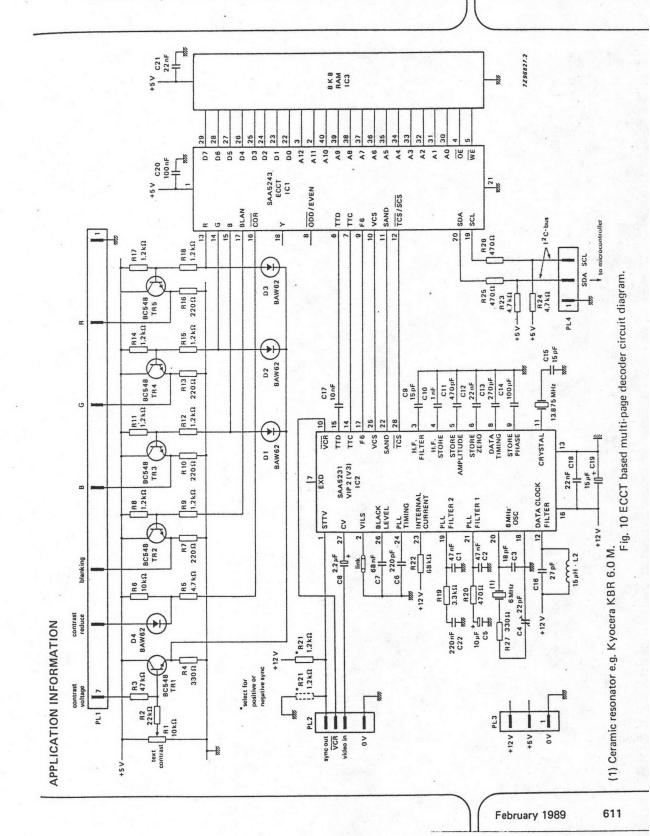

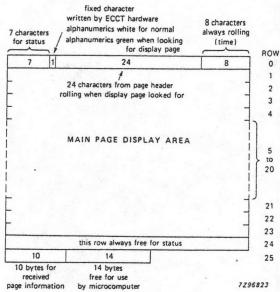

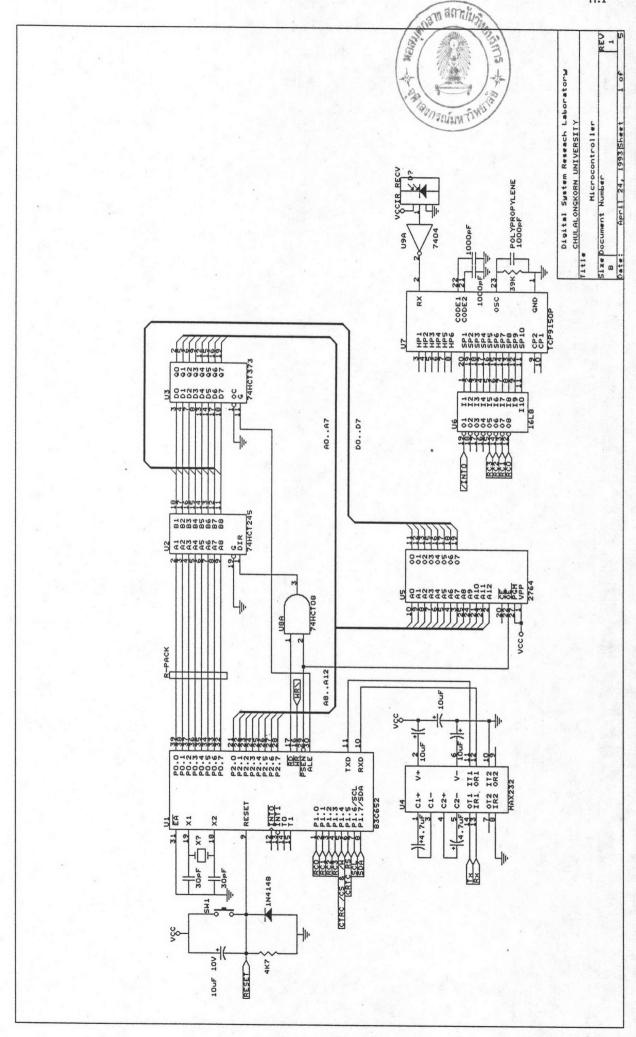

# ENHANCED COMPUTER CONTROLLED TELETEXT CIRCUITS (ECCT)

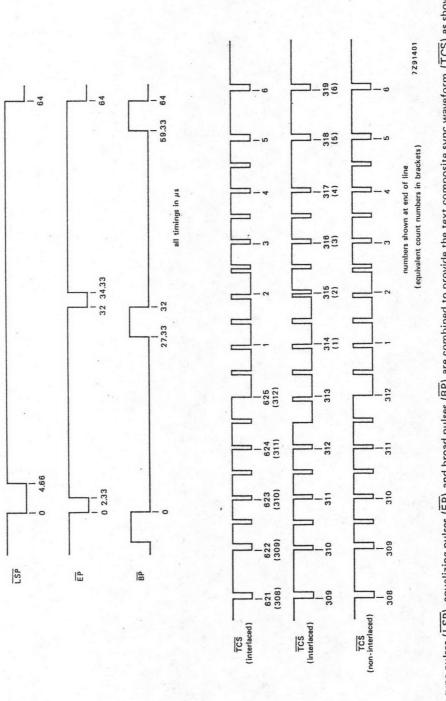

#### **GENERAL DESCRIPTION**

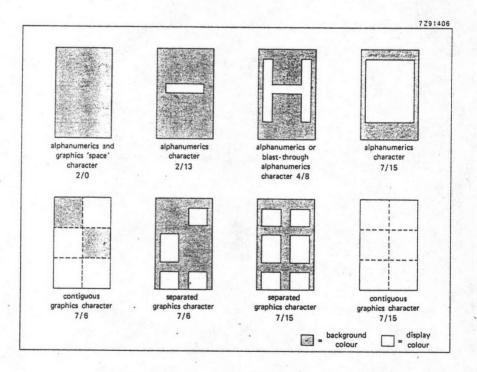

The SAA5243 series are MOS N-channel integrated circuits which perform all the digital logic functions of a 625-line World System Teletext decoder. The SAA5243 series operate in conjunction with the teletext video processor SAA5231, standard static RAMs and are controlled via the 2-wire I<sup>2</sup>C-bus. The devices can be used to provide videotex display conforming to a serial character attribute protocol.

#### **Features**

- Microcomputer controlled for flexibility

- High quality flicker-free display using a 12 x 10 character matrix

- Field flyback (lines 2 to 22), or full channel (all lines) data acquisition

- Up to four simultaneous page requests enabling acquisition during one magazine cycle

- Direct interface up to 8 K bytes static RAM

- Automatic language section of up to seven different languages

- 25th display row for software generated status messages

- Cursor control for videotex/telesoftware

- 7-bits parity or 8-bit data acquisition

- Extension packet reception option

- Standard I<sup>2</sup>C-bus slave transceiver (slave address 0010001)

- Single 5 volt power supply

- Mask programmable character sets

- Slave sync mode operation

- Odd/even field output for de-interlaced displays

Fig.1 Block diagram.

PACKAGE OUTLINE 40-lead DIL; plastic (SOT129).

## ORDERING INFORMATION

| type number   | version                      |

|---------------|------------------------------|

| SAA5243P/E/M2 | West European languages      |

| SAA5243P/H    | East European languages      |

| SAA5243P/K    | Arabic and English languages |

| SAA5243P/L    | Arabic and Hebrew languages  |

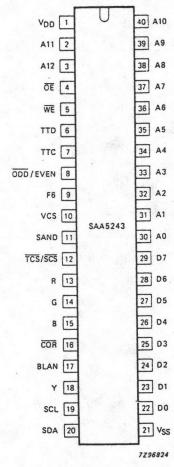

Fig.2 Pinning diagram.

### PINNING

1 V<sub>DD</sub> 2, 3, 40 A11, A12, A10

ŌĒ

Power supply: + 5 V power supply pin.

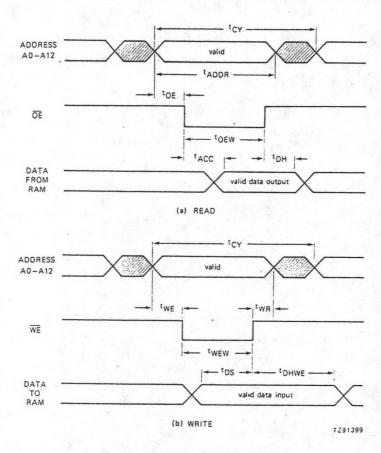

Chapter Address: three outputs that select which 1 K byte chapter of external RAM is being accessed for any read or write cycle.

Output Enable: active low output signal used to control the reading of the external RAM. It occurs continuously at a 1 MHz rate.

| 5          | WE .            | Write Enable: active low output signal used to control the writing of data to the external RAM. It occurs for a valid write cycle only and is interleaved with the read cycles.                                                                                                                                                                       |

|------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

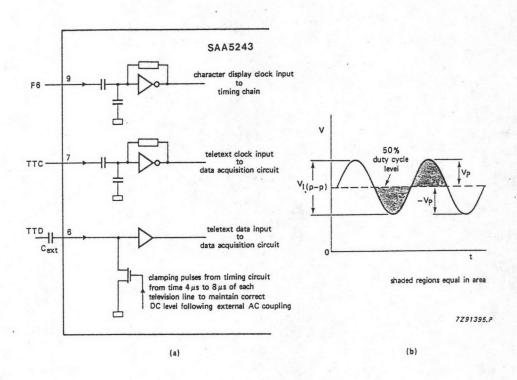

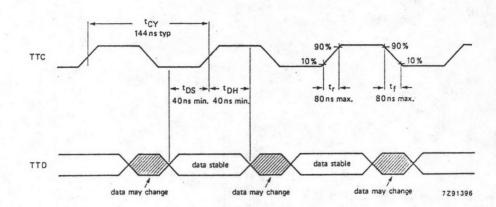

| 6          | TTD             | Teletext Data: input from the SAA5231 Video Input Processor (VIP2). It is clamped to $V_{SS}$ for 4 to 8 $\mu s$ of each television line to maintain the correct DC level following the external AC coupling.                                                                                                                                         |

| 7          | TTC             | Teletext Clock: 6.9375 MHz clock input from the SAA5231. It is internally AC coupled to an active clamp input buffer.                                                                                                                                                                                                                                 |

| 8          | ODD/EVEN        | $\overline{\text{Odd}}/\text{Even}$ : for interlaced mode, the output changes once per field at 2 $\mu$ s before the end of line 311 (624). The output is high for even fields and low for odd fields.                                                                                                                                                |

| 9          | F6              | Character display clock: 6 MHz clock input from the SAA5231. It is internally AC coupled to an active clamp input buffer.                                                                                                                                                                                                                             |

| 10         | VCS             | Video Composite Sync: input from the SAA5231 derived from the incoming video signal. Sync pulses are active high.                                                                                                                                                                                                                                     |

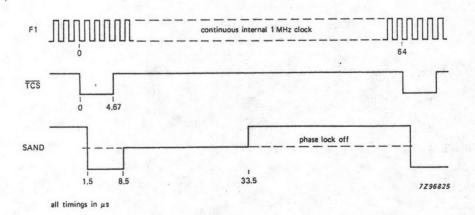

| 11         | SAND            | Sandcastle: 3-level sandcastle output to the SAA5231 containing the phase locking and colour burst blanking information.                                                                                                                                                                                                                              |

| 12         | TCS/SCS         | Text Composite Sync/Scan Composite Sync: as an output an active low composite sync waveform (TCS) with interlaced or non-interlaced format (see Fig.6) which is fed to the SAA5231 to drive the display timebases. Alternatively this pin can act as an input for an active low composite sync waveform (SCS) to 'slave' the display timing circuits. |

| 13, 14, 15 | R, G, B         | Red, Green, Blue: these 3 open drain outputs are the character video signals to the television display circuits. They are active high and contain character and background information.                                                                                                                                                               |

| 16         | COR             | Contrast Reduction: open drain, active low output which allows selective contrast reduction of the television picture to enhance a mixed mode display.                                                                                                                                                                                                |

| 17         | BLAN            | Blanking: open drain, active high output which controls the blanking of the television picture for a normal text display and for a mixed display.                                                                                                                                                                                                     |

| 18         | Y               | Character foreground: open drain, active high video output signal containing all the foreground information displayed on the television screen (e.g. for driving a display printer).                                                                                                                                                                  |

| 19         | SCL             | Serial Clock: input signal which is the I <sup>2</sup> C-bus clock from the microcontroller.                                                                                                                                                                                                                                                          |

| 20         | SDA             | Serial Data: is the I <sup>2</sup> C-bus data line. It is an input/output function with an open drain output.                                                                                                                                                                                                                                         |

| 21         | V <sub>SS</sub> | Ground: 0 volts.                                                                                                                                                                                                                                                                                                                                      |

| 22-29      | DO-D7           | 8 RAM data lines: 3-state input/output pins which carry the data bytes to and from the external RAM.                                                                                                                                                                                                                                                  |

| 30-39      | A0-A9           | RAM address: 10 output signals that determine which byte location within a 1 K byte chapter of external RAM is accessed for any read or write cycle.                                                                                                                                                                                                  |

## RATINGS

Limiting values in accordance with the Absolute Maximum System (IEC 134)

| parameter                                                              | conditions | symbol           | min. | max. | unit |

|------------------------------------------------------------------------|------------|------------------|------|------|------|